## EGC442 Class Notes 3/28/2023

**Baback Izadi** Division of Engineering Programs bai@engr.newpaltz.edu

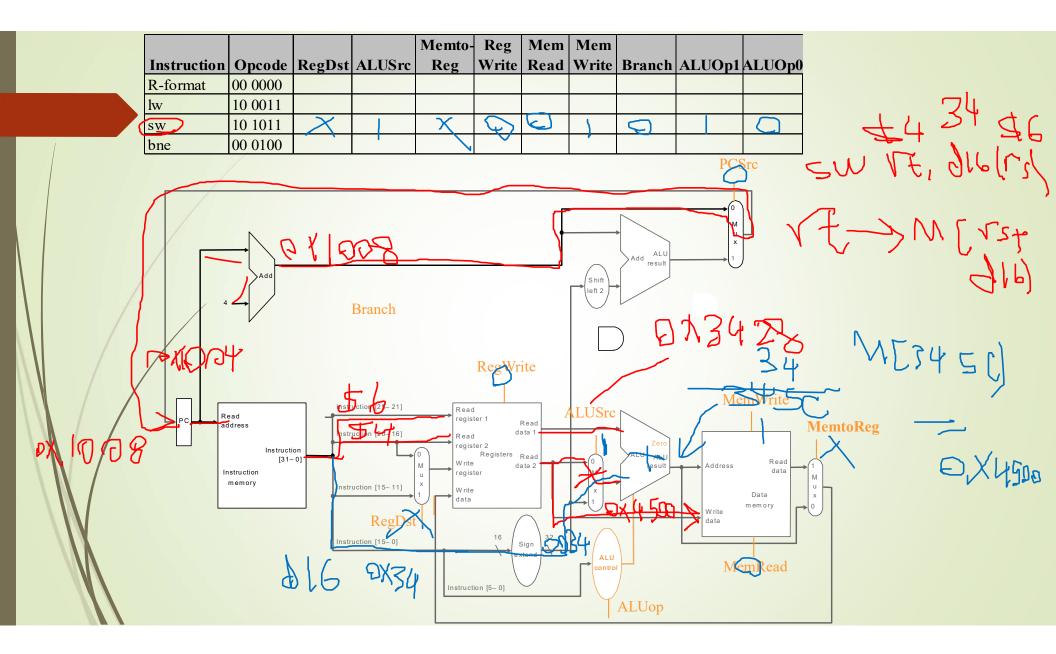

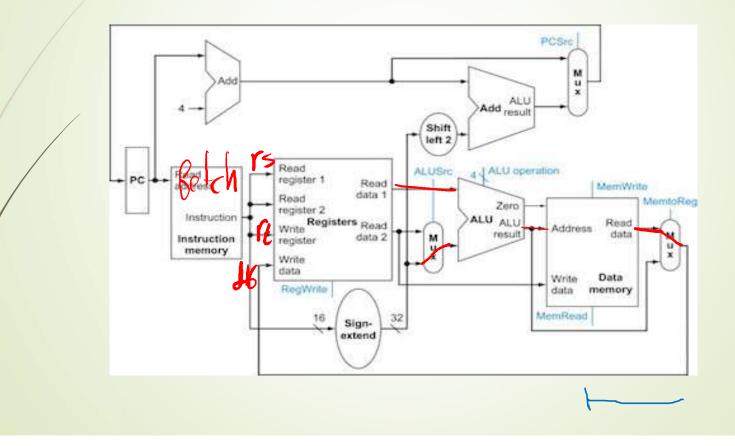

## la Ft, 216 (rs)

Which of the following is correct for a load instruction?

- MentoReg should be set to cause the data from memory to be sent to the register file.

- MemtoReg should be set to cause the correct register destination to be sent to the register file.

- We do not care about the setting of MemtoReg for loads.

The single-cycle datapath conceptually described in this section *must* have separate instruction and data memories, because \_\_\_\_\_.

the formats of data and instructions are different in MIPS, and hence different memories are needed

having separate memories is less expensive the processor operates in one cycle

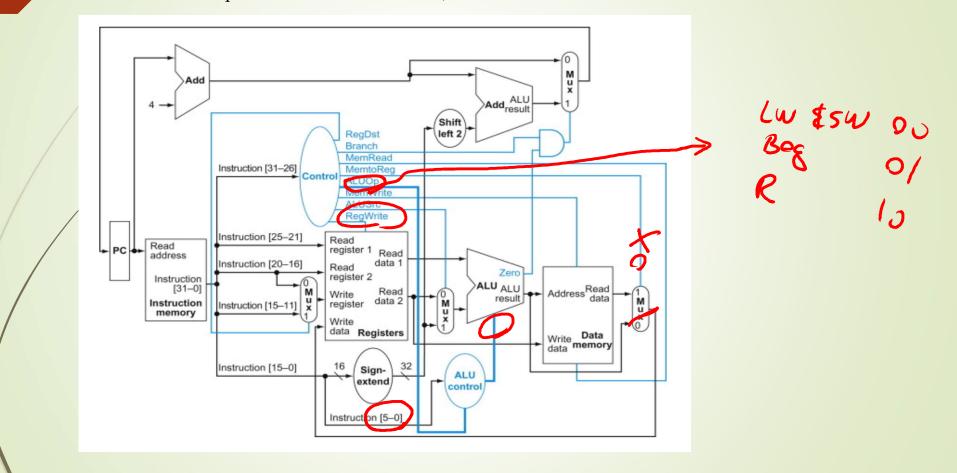

1) If the instruction is SW, then ALUOp should be \_\_\_\_\_. 00 01 10 unknown 1) If the instruction is SW, then the ALU's four control inputs should be  $\swarrow$ 0000 0010 1) For LW and SW instructions, the ALU function \_\_\_\_\_\_ Momory address

is the same

differs

1) If the instruction is OR, then ALUOp should be \_\_\_\_\_\_ R\_\_\_\_ Hype 10 unknown

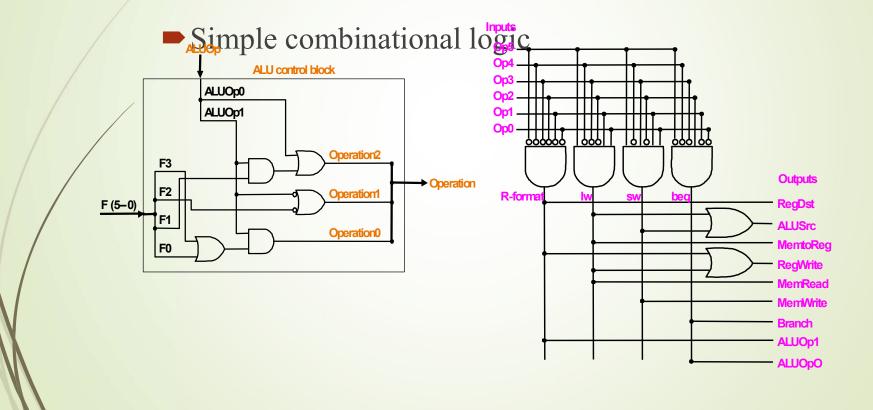

1) If the instruction is OR, then as well as examining the ALUOp bits, the ALU control will also examine

Instruction[31:26] (the leftmost bits)

- Instruction[5:0] (the rightmost bits) Function Real 1) If the instruction is OR, then the ALU control will (after examining the ALUOp and funct bits)

- output

10

0000 ALU designed 0001

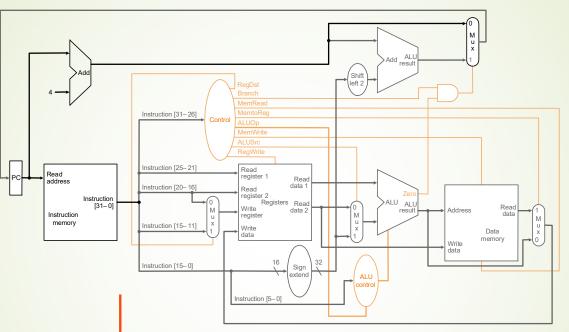

Consider the datapath and control unit below,

```

The control unit sends bits to the ALU control.

1)

0

1) The control unit enables a write to the register file using the signal.

RegDst

MemWrite

RegWrite

1) When MemToReg is 0, the data appearing at the register file's data input comes from the _____.

ALU's output

data memory's output

register file's output

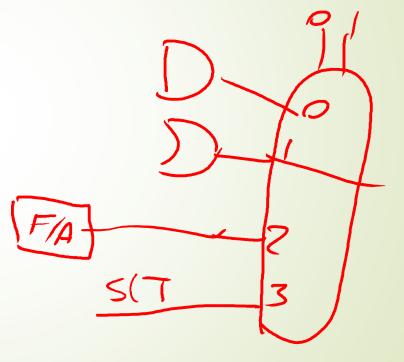

1) The ALU's top input always comes from the Read data 1 output of the register file. The ALU's bottom input can come from two possible places: The Read data 2 output of the register file, or the instruction's lower 16 bits, sign extended to 32 bits. Which control unit output select among those two places?

ALUOp

ALUSrc

Zero

13) The control unit's Branch output will be 1 for a branch equal instruction. However, the branch's target address is only loaded

into the PC if the ALU's Zero output is _____. Otherwise, PC is loaded with PC + 4.

0

```

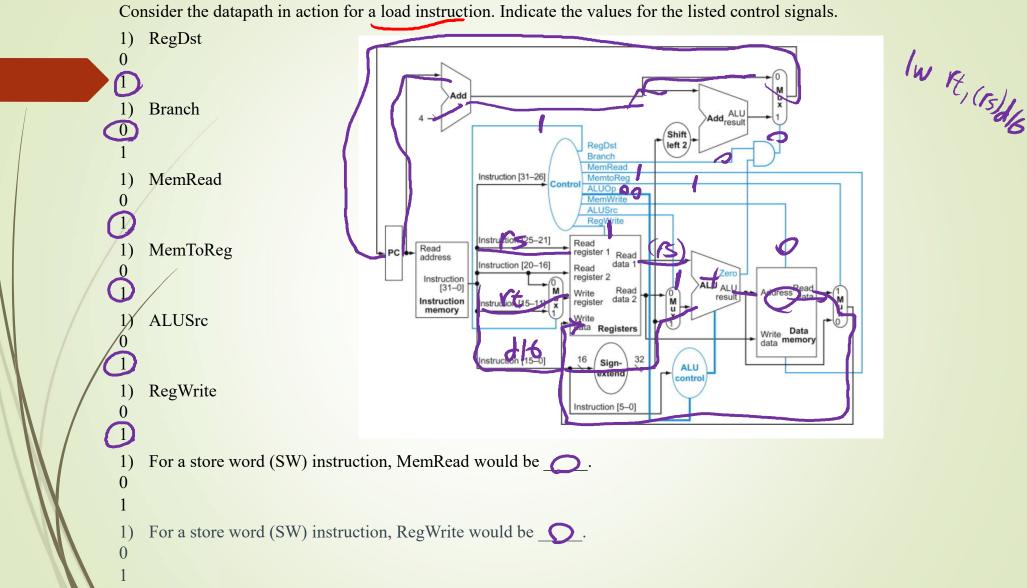

Consider the figure below showing control unit outputs for four kinds of instructions, using four rows (Rows 1, 2, 3, and 4).

| Instruction | RegDst | ALUSrc<br>0 | Memto-<br>Reg | Reg-<br>Write | Mem-<br>Read |     | Branch<br>0 | 1.0000 | ALU000 |  |

|-------------|--------|-------------|---------------|---------------|--------------|-----|-------------|--------|--------|--|

| R-format    | 1      |             | 0             |               | 0            | 0   |             |        | 0      |  |

| 1w          | 0      | 1           | 1             | 1             | 1            | 0   | 0           | 0      | 0      |  |

| SW          | Х      | 1           | Х             | 0             | 0            | (1) | 0           | 0      | 0      |  |

| beq         | х      | 0           | X             | 0             | 0            | 0   | 1           | 0      | 1      |  |

1) In Row 1, RegWrite is 1, meaning the register is always written for an R-type instruction.

1) In Row 1, the last two bits, ALUOp, are 10, meaning the ALU will perform an add function,

toute into

R-type

True False

load word

True

False

True False

In beq's Row 4, MemToReg is X because the value appearing at the register file's Write data input is irrelevant.

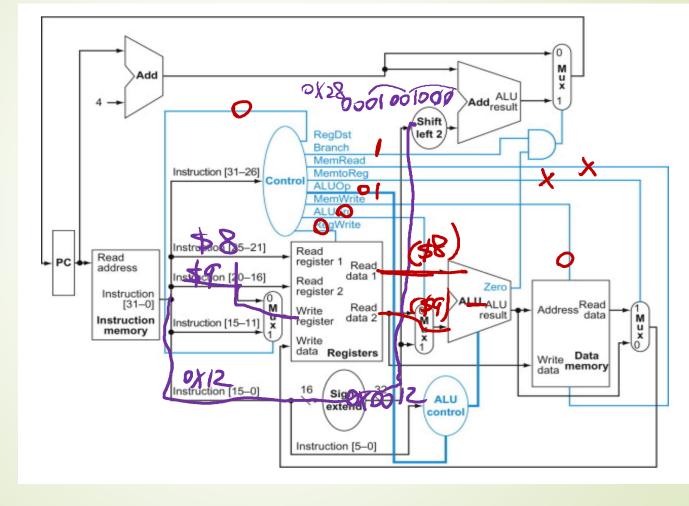

Highlight the active paths and assign values to the control signals of the following for

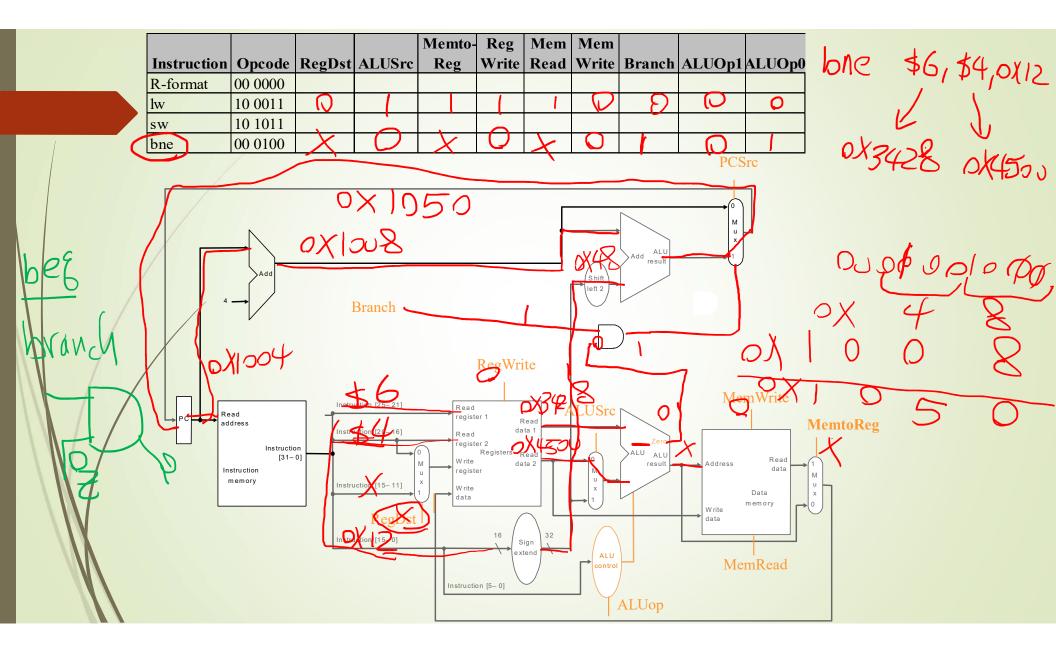

a. beq \$8, \$9, 0x12

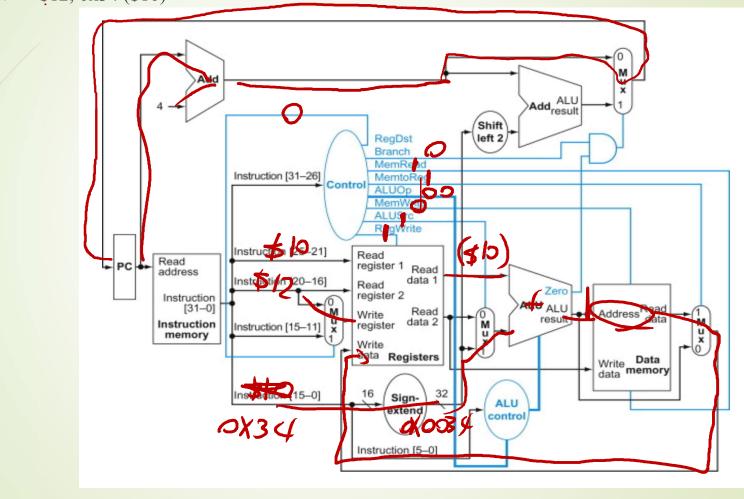

Highlight the active paths and assign values to the control signals of the following for

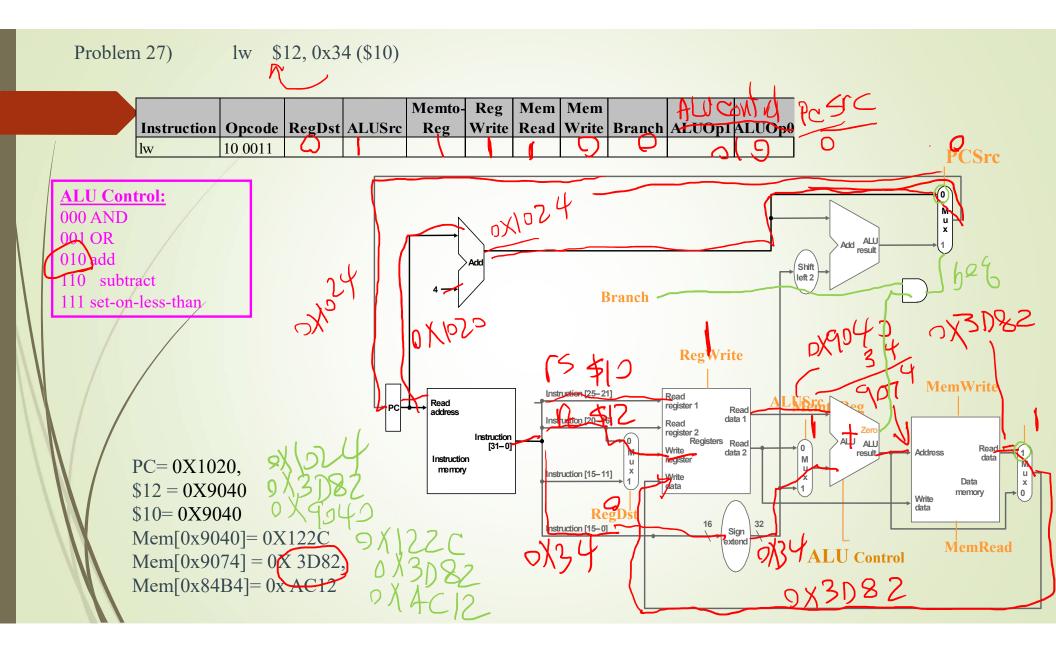

a. lw \$12, 0x34 (\$10)

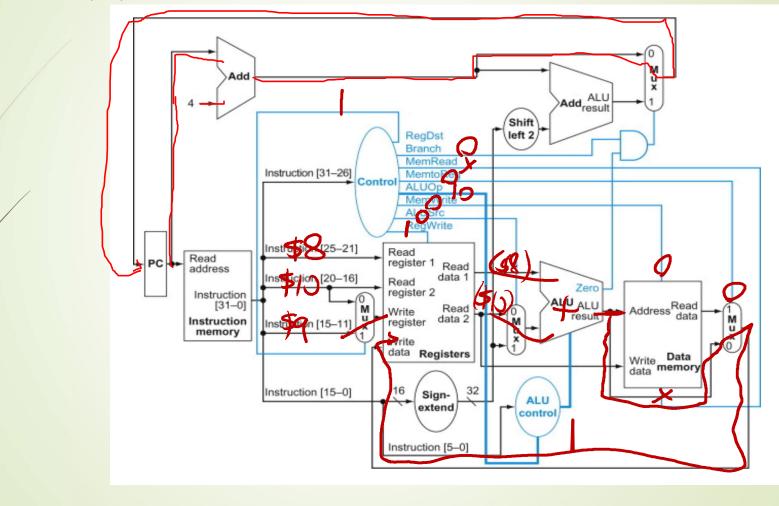

Highlight the active paths and assign values to the control signals of the following for

add \$9, \$8, \$10

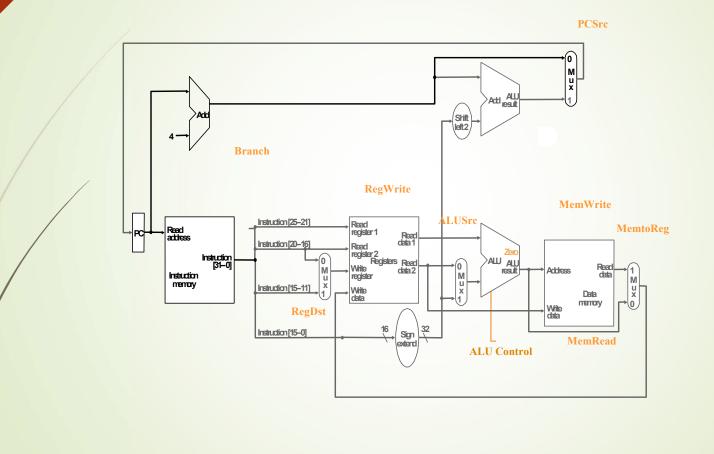

## Control

|             |         |        |        | Memto- | Reg   | Mem  | Mem   |        |        |        |

|-------------|---------|--------|--------|--------|-------|------|-------|--------|--------|--------|

| Instruction | Opcode  | RegDst | ALUSrc | Reg    | Write | Read | Write | Branch | ALUOp1 | ALUOp0 |

| R-format    | 00 0000 | 1      | 0      | 0      | 1     | 0    | 0     | 0      | 1      | 0      |

| lw          | 10 0011 | 0      | 1      | 1      | 1     | 1    | 0     | 0      | 0      | 0      |

| sw          | 10 1011 | Х      | 1      | Х      | 0     | 0    | 1     | 0      | 0      | 0      |

| beq         | 00 0100 | Х      | 0      | Х      | 0     | 0    | 0     | 1      | 0      | 1      |